EP104

10 6 月, 2019EP105

10 6 月, 2019Part Number:EP103T

Overview

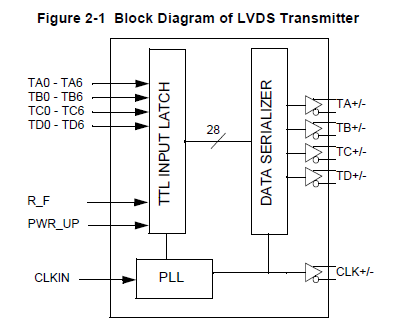

The EP103T LVDS transmitter supports transmission between the host and the flat panel display up to SXGA+ resolutions. The transmitter converts 25 bits (8-bits/color, 2 dummy bits) of Low Voltage TTL data and 3 control bits into 4 LVDS (Low Voltage Differential Signal) data streams. At a maximum input clock rate of 135MHz, each LVDS differential data pair speed is 945Mbps, providing a total throughput of 3.78Gbps. The transmitter can be configured to input clock rising edge or falling edge strobe through an external pin.

Features

The EP103T includes the following distinctive features:

•Support 10MHz to 135MHz clock rates for HVGA to SXGA+ resolution

•Up to 3.78Gbps bandwidth

•PLL requires no external components

•Cycle-to-cycle jitter rejection

•3.3V to 1.8V Low Voltage TTL tolerant Input

•Programmable data and control strobe select

•Power down mode supported

•TSSOP package (8.1mm x 14mm)

Block Diagram