EP102C

10 6 月, 2019EP103T

10 6 月, 2019Part Number:EP104

Overview

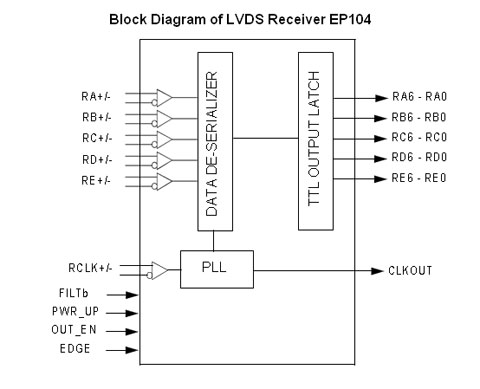

The EP104 supports single link transmission between the host and the flat panel display up to SXGA+ resolution. The EP104 converts the LVDS differential inputs into 35-bits control and data outputs. Also,the output data can be aligned to the rising or the falling edge of the output clock.

Features

The EP104 includes the following distinctive features:

• Supports clock range from 8MHz to 90MHz

• PLL requires no external components

• Output Clock Edge Programmable

• Power Down Mode

• Compatible with THine THC63LVD104

• Single 3.3V CMOS design

• 64-pin LQFP (Pb-free)

Block Diagram